| Score: | Name: |

|--------|-------|

|        |       |

|        |       |

## ECE 3055 Quiz Wednesday, March 25

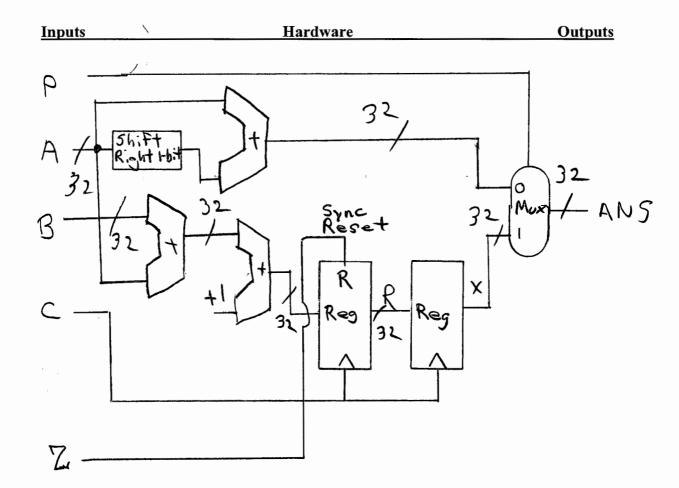

In the space below, draw a block diagram of the hardware synthesized by the VHDL code found on the additional page provided with the quiz. In the block diagram, include the following:

- 1. Show all input signals on the left and outputs on the right.

- 2. Draw each hardware unit in a style similar to the textbook's block diagrams.

- 3. Include and clearly indicate any registers, clock signals, and resets.

- 4. Label all signals with their VHDL signal name (both internal and external).

- 5. Use a "/" with a number to indicate the width of any busses (more than 1-bit).

- 6. Number each of the mux's input signals with it's corresponding decimal number (i.e. the value on the mux's control input signal that selects each input).

- 7. Indicate # of bits and direction for any shifts and indicate if resets are sync or async.

```

LIBRARY IEEE:

USE IEEE.STD LOGIC 1164.ALL;

USE IEEE.STD LOGIC ARITH.ALL;

USE IEEE.STD_LOGIC_SIGNED.ALL;

ENTITY test10 IS

PORT( A, B : IN STD_LOGIC_VECTOR( 31 DOWNTO 0 );

P, C, Z : IN STD LOGIC;

ANS : OUT STD_LOGIC_VECTOR( 31 DOWNTO 0 ));

END test10:

ARCHITECTURE behavior OF test10 IS

SIGNAL X, S, K, R: STD LOGIC VECTOR(31 DOWNTO 0);

BEGIN

ANS \leq X WHEN P = '1' ELSE A + S;

S <= '0' & A(31 DOWNTO 1);

K \le A + B:

PROCESS

BEGIN

WAIT UNTIL C'EVENT AND C='1';

IF Z='1' THEN R <= X"00000000";

ELSE

R \le K + 1;

END IF;

X \leq R;

END PROCESS;

END behavior;

```