| Score: | Name: |  |

|--------|-------|--|

|        |       |  |

## ECE 3055 Quiz Wednesday, September 31

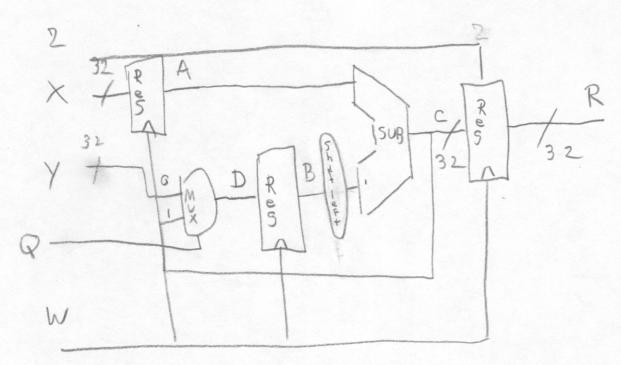

In the space below, draw a block diagram of the hardware synthesized by the VHDL code found on the additional page provided with the quiz. In the block diagram, include the following:

1. Show all input signals on the left and outputs on the right.

2. Draw each hardware unit in a style similar to the textbook's block diagrams.

3. Include and clearly indicate any registers, clock signals, and resets.

4. Label all signals with their VHDL signal name (both internal and external).5. Use a "/" with a number to indicate the width of any busses (more than 1-bit).

6. Number each of the mux's input signals with it's corresponding decimal number (i.e. the value on the mux's control input signal that selects each input).

Inputs Hardware Outputs

Sub 1 pt Mux 2 Register 1 A 1 Clock, Reset 1 I/Osignals 1 Shift 1 Bus width 1

```

ENTITY test5 IS

PORT(X, Y : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

Q, W, Z : IN STD_LOGIC;

: OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END test5;

ARCHITECTURE behavior OF test5 IS

SIGNAL A, B, C, D: STD LOGIC VECTOR(31 DOWNTO 0);

D <= C WHEN Q='1' ELSE Y;

C \le A - (B(30 \text{ DOWNTO } 0) \& "0");

PROCESS

BEGIN

WAIT UNTIL W'EVENT AND W='1':

R \leq C;

END IF;

A \leq = X;

B \leq D;

END PROCESS;

END behavior;

```