| Score:Name:                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ECE 3055 Test 1                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1. (20 <i>points</i> ) Compare the execution time of the program below on the three MIPS hardware models studied in class.                                                                                                                                                                                                                                                      |  |  |  |

| sw $\$2,100(\$0)$ 4<br>lw $\$3,200(\$0)$ 5<br>or $\$4,\$5,\$7$ 4<br>add $\$8,\$7,\$5$ 4                                                                                                                                                                                                                                                                                         |  |  |  |

| Part 1: A single clock cycle MIPS with a clock cycle time of 40ns would take                                                                                                                                                                                                                                                                                                    |  |  |  |

| $\frac{160}{60}$ ns to execute the program.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Part 2: The multi clock cycle model of the MIPS with a clock cycle time of 30ns would take                                                                                                                                                                                                                                                                                      |  |  |  |

| 510 ns to execute the program.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Part 4: The pipelined MIPS model with data forwarding and hazard detection and a clock                                                                                                                                                                                                                                                                                          |  |  |  |

| cycle time of 10ns would require <u>46</u> ns to execute the program. Assume a register will write and read correctly during the same clock cycle. Do not include the time required to fill and flush the pipeline.                                                                                                                                                             |  |  |  |

| Part 5: If the pipelined MIPS model started this program immediately after powering up,                                                                                                                                                                                                                                                                                         |  |  |  |

| it would take 80 ns. This includes the time required to fill and flush the pipeline.                                                                                                                                                                                                                                                                                            |  |  |  |

| 2. (5 Points) The Pentium 4 has a faster clock cycle time than the PIII. What main change in the architecture (i.e. not just a faster transistor technology) increased the clock cycle time. What is the potential performance loss in this new architecture that must be addressed?  deeper pipelines (20 us. 10), Needs better branch prediction or it will have more stalls. |  |  |  |

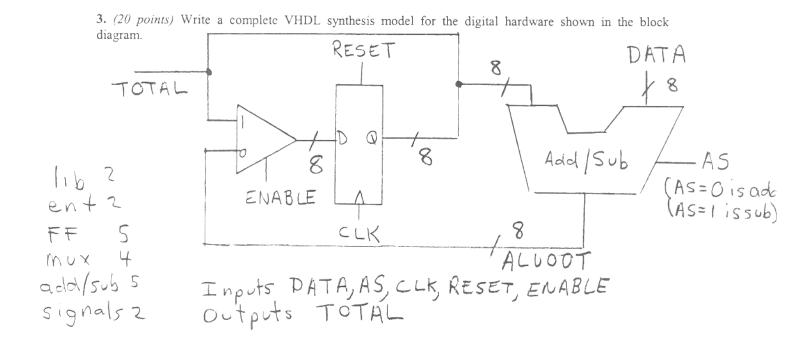

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;

IEEE.STD_LOGIC_UNSIGNED.all;

use

entity Problem3 is

AS, Clk, Reset, Enable: in std_logic;

Data: in std_logic_vector(7 downto 0);

Total: out std_logic_vector(7 downto 0));

port (

end Problem3;

architecture behavior of Problem3 is

signal total_int, ALUout: std_logic_vector(7 downto 0);

Total <= total_int;

ALUout <= Total_int + Data WHEN AS='0' ELSE Total_int - Data;

process

begin

WAIT UNTIL (CLK'EVENT and CLK='1');

IF reset = '1' THEN

total_int <= "00000000";

ELSE

IF (Enable ='1') THEN

total_int <= total_int;</pre>

total_int <= ALUout;

END IF;

END IF;

end process;

end behavior;

```

4. (30 points) The following sequence of MIPS instructions is clocked into the pipeline shown on page 472-476. Examine this figure carefully to see exactly where each signal is located (i.e. before or after pipeline registers). After Clock cycle 5, Indicate the resulting register values in the spaces provided below. All numbers are in hex. Memory location 1 contains 0x55555555. Assume that each register contains a value equal to the register number prior to execution of this code.

| add  | \$2,\$5,\$6 |

|------|-------------|

| lw   | \$2,1       |

| sub  | \$3,\$1,\$4 |

| andi | \$6,\$7,8   |

| add  | \$4,\$3,\$0 |

| loop:                        | sw<br>lw<br>sub<br>and<br>add<br>or<br>sw<br>beq | \$2,100(\$0)<br>\$5,200(\$2)<br>\$6,\$5,\$2<br>\$8,\$3,\$6<br>\$8,\$5,\$8<br>\$8,\$3,\$8<br>\$5,100(\$6)<br>\$6,\$0,loop |                                                                                                                                                                                                           |

|------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| compar<br>of NOI<br>instruct | e circuit<br>P instructions. As                  | , or automatic branch flushing.<br>tions to eliminate all potential<br>sume other non-NOP instruction                    | Rewrite the code sequence by adding the minimum number data and branch hazards – do not change the order of the ns follow the branch in the original code sequence above.                                 |

| 1 1                          | #                                                | 2, [00(\$0)<br>5, 200(\$2)                                                                                               | add \$8,\$5,\$8                                                                                                                                                                                           |

| no<br>no<br>su               |                                                  | 6,\$5,\$2                                                                                                                | nop<br>or<br>or<br>\$8,\$3,\$8<br>su \$5,100(\$6)<br>beq \$6,\$0,100p                                                                                                                                     |

| 110                          | P                                                | t8,#3,#G                                                                                                                 | 1100                                                                                                                                                                                                      |

| 9110                         | P                                                |                                                                                                                          | nop3 no new branch compare!                                                                                                                                                                               |

| outlined<br>cycles 1         | d in the t<br>required                           | ext, and adding a branch compa                                                                                           | is improved by adding the hazard and forwarding unit as are unit to the decode stage. Determine the number of clock ation (i.e. executes code in loop and branches back to top of priginal code sequence. |

|                              | were no<br>for execu                             |                                                                                                                          | original program would require 2 clock 5 + 7                                                                                                                                                              |

| But the clock c              | program<br>ycles is r                            | stalls and/or flushes the pipelinequired for execution.                                                                  | ne clock cycles so a total of /                                                                                                                                                                           |

|                              |                                                  |                                                                                                                          |                                                                                                                                                                                                           |

|                              |                                                  |                                                                                                                          |                                                                                                                                                                                                           |

**5.** (25 points) The program below is executed on the 5 stage pipelined MIPS described in chapter 6. Answer the following questions about this program.